芯片资讯

-

01

2024-01

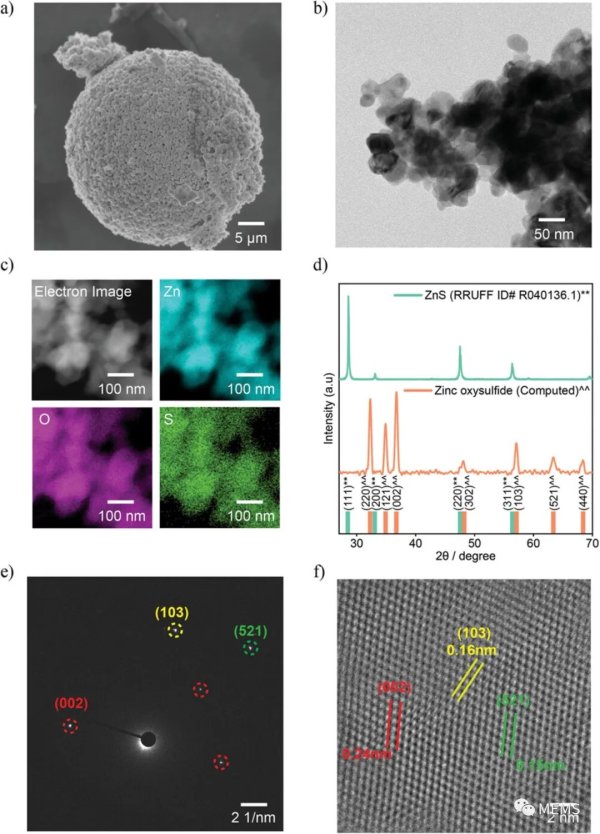

基于超薄氧硫化锌的室温高性能NO₂气体传感器

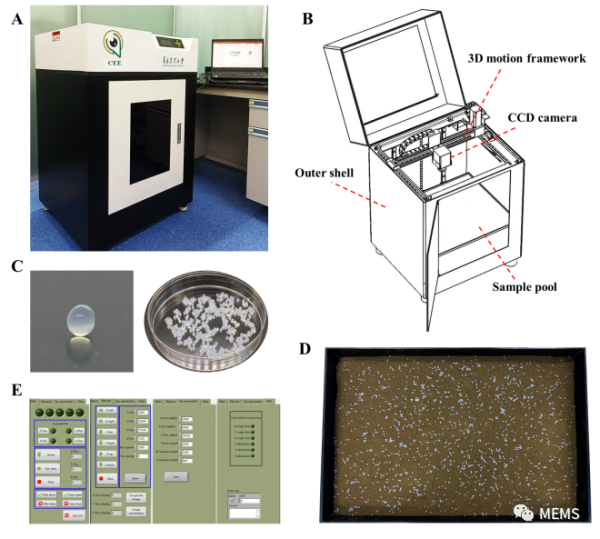

金属氧硫化物是一类新兴的用于高性能二氧化氮(NO₂)气体传感的敏感材料,因为它们具有室温工作能力、优异的NO₂选择性、ppb级的检测极限以及对周围环境的高稳定性。 据麦姆斯咨询报道,近日,墨尔本皇家理工大学(RMIT University)的科研人员研究了由超薄纳米片制成的三维自组装氧硫化锌的室温NO₂传感性能。在460 nm激发下,该传感器在室温下对1.26 ppm NO₂气体表现出完全可逆和可重复的传感响应,响应幅度约为2.27,检测限(LOD)为294.8 ppt。这项工作证明了金属氧硫

-

31

2023-12

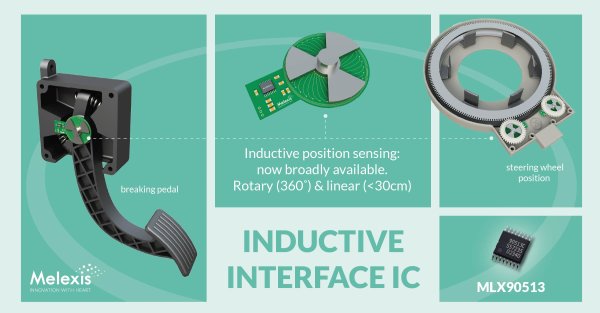

Melexis新款传感器将促进高精度位置感应应用的大范围普及

全球微电子工程公司Melexis近日宣布,推出具备出色精度的电感式传感器芯片MLX90513,专为汽车踏板和转向应用而设计。得益于MLX90513,这种优异的性能不再仅限于少数应用。这款传感器接口芯片达到ASIL C等级,具有片上数字信号处理功能,可增强零延迟性能。 对于许多需要位置感应的应用,高精度与完全抗杂散磁场的结合可实现无与伦比的性能,充分满足现有应用的需求。 性能Melexis推出的全新位置传感器芯片MLX90513可提供±0.1%的满量程精度(在360°范围内的旋转式实现方式中为±

-

31

2023-12

FPGA如何抵抗单粒子效应?

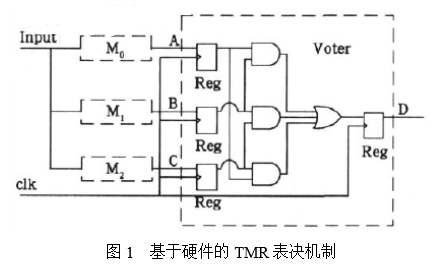

21世纪太空将成为国际军事竞争的制高点。随着技术的发展和科技的进步,航天电子设备对诸如现场可编程门阵列(Field Programmable Gate Array, FPGA)、数字信号处理器(Digital Signal Processor, DSP)等超大规模集成电路的依赖性越来越强。另一方面,宇宙中存在各种辐射射线,使得高性能芯片受太空射线影响而产生单粒子效应的概率大大提高,并且器件的集成度越高,单粒子效应的影响就越显著,这严重影响和制约着航天电子仪器设备的正常工作。因此开发具有高速度、

-

31

2023-12

驻车雷达起什么作用 驻车雷达和倒车影像的区别

驻车雷达起什么作用 驻车雷达是一种用于辅助车辆停车的技术,主要起到以下几个作用: 1. 障碍物检测:驻车雷达可以检测到车辆周围的障碍物,如墙壁、柱子、其他车辆等。它使用超声波或雷达技术发送信号并接收回波,从而测量与障碍物的距离。当靠近障碍物时,雷达会发出警告信号,提醒驾驶员注意。 2. 距离提示:驻车雷达还可以提供距离提示,以帮助驾驶员判断离障碍物的距离。通常,雷达系统会通过声音或视觉信号(例如显示屏上的图标或数字)向驾驶员显示离障碍物的距离,帮助驾驶员做出适当的操控。 3. 视角补充:驻车雷

-

31

2023-12

两个栈实现一个队列方法

栈和队列是比较基础的数据结构。无论在工作中,还是在面试中,栈和队列都用的比较多。在计算机的世界,你会看到队列和栈,无处不在。 栈:一个先进后出的数据结构 队列:一个先进先出的数据结构 栈和队列这两种数据结构,同时也存在某种联系。用栈可以实现队列,用队列也可以实现栈。 两个栈实现一个队列 思路:让数据入stack1,然后栈stack1中的数据出栈并入到栈stack2,然后出stack2。 代码如下: type CQueue struct { stack1, stack2 *list.List}/

-

31

2023-12

FPGA设计中的模块化设计

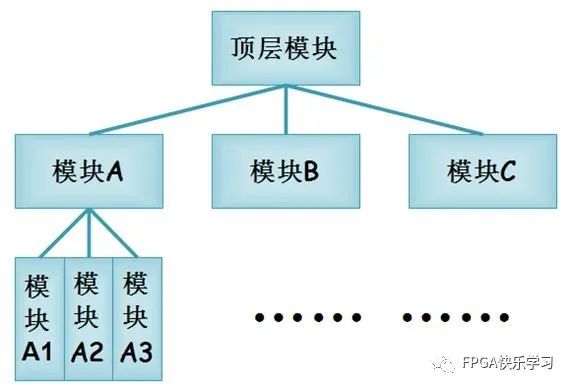

模块化设计是FPGA设计中一个很重要的技巧,它能够使一个大型设计的分工协作、仿真测试更加容易,代码维护或升级也更加便利。 如图3.28所示,一般整个设计工程的顶层文件里只做例化,不做逻辑处理。顶层模块下会包含多个子模块,比如图中的模块A、模块B、模块C等等,而模块A、B、C下又可以再为分多个子模块实现,如A模块可以包含子模块A1、A2和A3等。 图3.28 模块设计示意图 采用模块化的设计,就可以将大规模复杂系统按照一定规则划分成若干模块,然后对每个模块分别进行设计输入、综合与实现

-

31

2023-12

毫米波雷达如何测量速度和位置 毫米波雷达和超声波雷达有什么区别

毫米波雷达测试铁片的原理 毫米波雷达是一种利用毫米波进行物体探测和测距的传感技术。它使用的频率范围通常位于30 GHz到300 GHz之间。 对于测试铁片的原理,毫米波雷达可以通过以下步骤进行: 1. 信号发射:毫米波雷达会生成一个毫米波信号,并将其发射出去。这个信号通常是连续波或脉冲波。 2. 信号传播:发射的信号在空间中传播,并遇到待测试的铁片。 3. 反射:当毫米波遇到铁片时,一部分能量会被铁片吸收,而另一部分则会被反射回来。 4. 接收:毫米波雷达接收反射回来的信号,并将其转换成电信号

-

31

2023-12

基于FPGA系统Register和Memory的复位

Register 和 Memory 的复位 Register是有复位端口的,当我们assert复位端口,寄存器便被复位到0。 而FPGA中的Memory通常是没有复位端口的,假如我们想要clear memory中的内容,需要一行一行,一个地址一个地址去清除。如果没有memory clear的逻辑,那么之前写在memory中的数据会一直存在,直到整个FPGA上电复位。 一次Memory没有复位引起的歧义 首先我们的FPGA系统中有个feature是需要memory存储一些配置条件,这个配置条件是

-

31

2023-12

用于芳香族污染物高效检测的生物传感器

环境中芳香族污染物对人身安全及环境等都造成严重危害,而常规探测方式存在探测效率低、作业安全性差、易受干扰等瓶颈问题。因此,基于生物传感的芳香族污染物探测技术的发展具有重要战略和环保意义。芳香族污染物分子可以分解为多种化合物,其挥发后的主要蒸气成分包括2,4-二硝基甲苯(2,4-DNT)和1,3-二硝基苯(1,3-DNB)。因此,结合1,3-DNB和2,4-DNT检测的生物传感器可以更准确、更高效地应用于芳香族污染物的探测。 然而,目前以1,3-DNB为响应物的生物传感器的研究报道却很少。基于此

-

31

2023-12

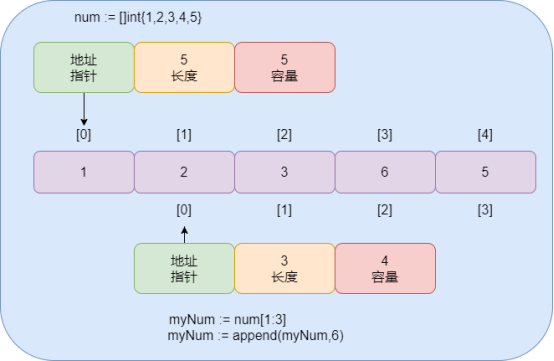

golan共享底层数组的切片

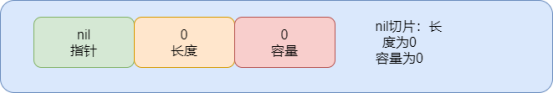

nil 和空切片 有时,程序可能需要声明一个值为 nil 的切片(也称nil切片)。只要在声明时不做任何初始化,就会创建一个 nil 切片。 var num []int 在 Golang 中,nil 切片是很常见的创建切片的方法。nil 切片可以用于很多标准库和内置函数。在需要描述一个不存在的切片时,nil 切片会很好用。比如,函数要求返回一个切片但是发生异常的时候。下图描述了 nil 切片的状态: 空切片和 nil 切片稍有不同,下面的代码分别通过 make() 函数和字面量的方式创建空切片:

-

31

2023-12

数组中如何增加切片的容量

切片扩容 相对于数组而言,使用切片的一个好处是:可以按需增加切片的容量。 Golang 内置的 append() 函数会处理增加长度时的所有操作细节。要使用 append() 函数,需要一个被操作的切片和一个要追加的值,当 append() 函数返回时,会返回一个包含修改结果的新切片。 函数 append() 总是会增加新切片的长度,而容量有可能会改变,也可能不会改变,这取决于被操作的切片的可用容量。 num := []int{1, 2, 3, 4, 5}// 创建新的切片,其长度为 2 个元素

-

31

2023-12

瑞萨面向高端工业传感器系统推出具备高速、 高精度模拟前端的32位RX MCU

全新RX23E-B相比现有版本数据速率快8倍,并包含125 kSPS ΔΣ A/D转换器 2023 年 11 月 22 日,中国北京讯 - 全球半导体解决方案供应商瑞萨电子(TSE:6723)今日宣布面向高端工业传感器系统推出一款全新RX产品——RX23E-B,扩展32位微控制器(MCU)产品线。新产品作为广受欢迎的RX产品家族的一员,具有高精度模拟前端(AFE),专为需要快速、精确模拟信号测量的系统而设计。 该新型MCU集成24位Delta-Sigma A/D转换器,转换速度高达125 k