芯片资讯

- 发布日期:2024-01-02 13:02 点击次数:103

1 ** 全数字高码率QPSK调制解调软件设计**

1.1 QPSK调制

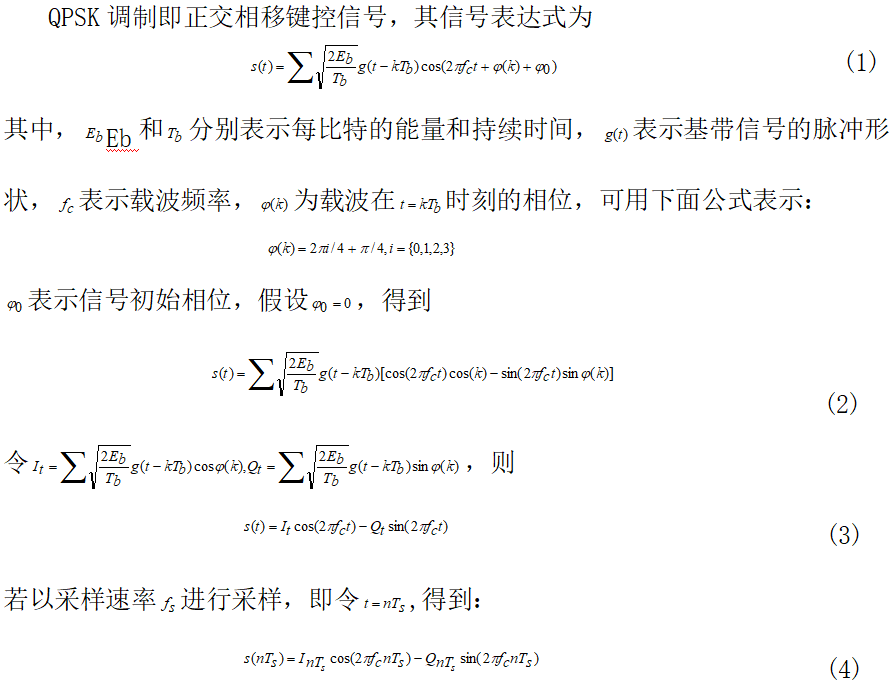

1.1.1 QPSK调制原理

1.1.2 QPSK并行调制实现

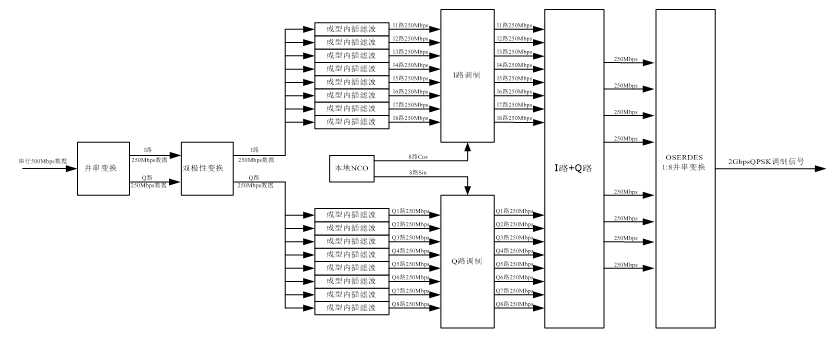

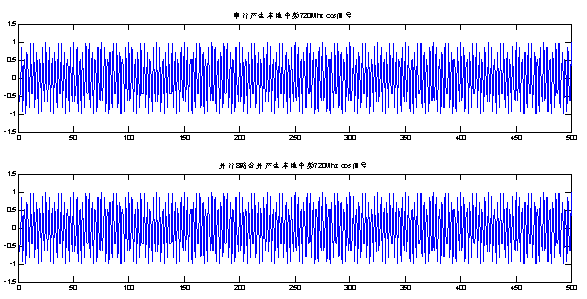

调制信号的符号速率达到500Mbps,根据奈奎斯特采样定理,DA的采样频率采用2Gbps。由于数据速率比较的高,对FPGA运算要求太高,因此在设计过程中,采用并行处理的方式,来减轻对FPGA运算的压力。图1-1为高码率500M QPSK调制实现框图。其实现的原理为将二进制数据流经过QPSK映射后形成I、Q两路基带信号,在经过8倍成型滤波器后,分别与两路正交的数字本振混频后相加输出至DAC即可。

图1-1 并行QPSK调制实现框图

1.1.2.1 QPSK符号映射

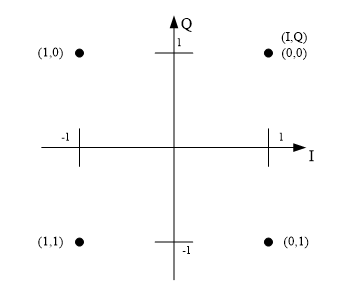

QPSK信号的每个码元包含两个比特信息,可用ab表示。ab序列有四种排列,即00,01,10,11。每种排列对应4种不同的调制相位。通常各种排列的相位关系按照格雷码进行编码,其符号映射关系如图1-2所示。

图1-2 QPSK映射星座图

在实现过程中,将每个符号所包含的两比特二进制信息,分别对应为I、Q两路,先到的信息比特映射为I路,后到的信息比特映射为Q路。其中二进制0对应正值(逻辑高+1),二进制1对应负值(逻辑低-1)。

图1-3为500Mbps QPSK调制MATLAB仿真映射星座图,从图中可以看出基带数据严格聚集在[-1,-1],[-1,1],[1,-1],[1,1]四个相位点上。

图1-3 500MbpsQPSK调制MATLAB仿真映射星座图

1.1.2.2数字基带成型滤波

由于现代无线电通信及卫星通信中,频带和功率一般均受限。一方面,为了有效利用信道,节约频谱资源,需要对发射信号进行带限;另一方面,当矩形脉冲通过带限信道时,脉冲会在时间上扩展,每个符号的脉冲将扩展到相邻符号的码元内,这会造成码间串扰(ISI),并导致接收机在检测码元时发生错误的概率增大。由于码间串扰是影响传输系统性能的主要因素之一,因此为了消除码间串扰,并有效利用带宽资源,需要对基带信号进行脉冲成型。

另外,从QPSK星座图可以看出, EEPROM带电可擦可编程存储器芯片大全信号的相位跳变是瞬时变化的, 电子元器件PDF资料大全会导致信号的频谱发生扩散。想要无失真地传输信号, ATMEGA系列ATMEL芯片COM必须增大信道的带宽, 芯片交易网IC交易网但是这样会降低信道利用率。因此需要采用基带滤波成型技术对QPSK符号的时域波形进行扩展,CMOS图像传感器集成电路芯片将QPSK信号频谱限制在一个合理的范围内。

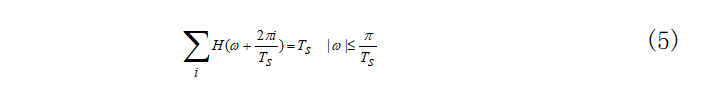

为了实现无码间串扰传输,基带传输频域总特性需要满足奈奎斯特第一准则,即:

其中,Ts为基带信号的符号周期,从式中可以看出,一个实际的H(ω)特性若能等效成一个矩形低通滤波器,则可实现无码间串扰。

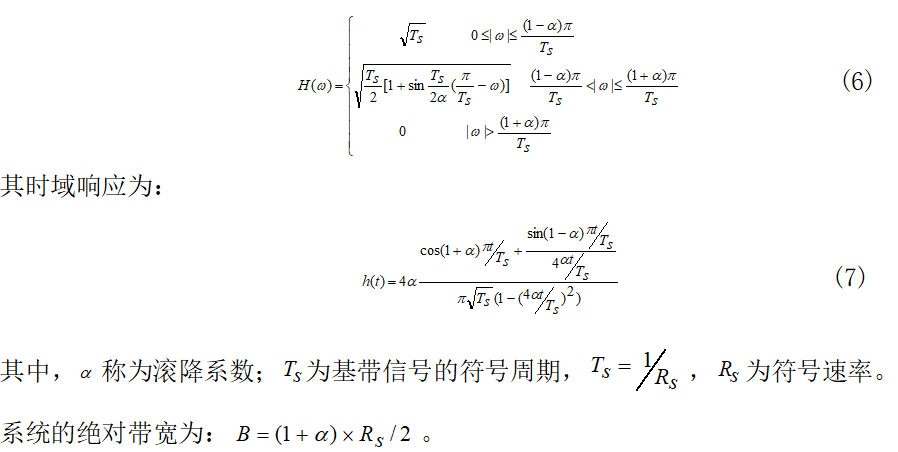

在实际的通信系统中,常采用平方根升余弦滚降滤波器实现,其H(ω)在滚降段中心频率处呈奇对称的振幅特性,可以满足奈奎斯特第一准则。该滚降滤波器具有匹配滤波的功能,可以克服理想低通滤波器设计困难,将过渡带设计的很平滑,还可以通过改变其滚降系数来设计符合要求的过渡带,改变传输信号成型波形,将信号频带限制在要求的频率范围之内,减小定时误差带来的影响,从而消除码间干扰。其频域响应为:

α取值一般范围为0.2~0.6。当α较大时,时域波形衰减快,并且震荡小,这有利于减小码间干扰和定时误差的影响,但是系统占用的频带变宽,ATMEGA系列-ATMEL芯片同时带内噪声对信号的影响也会加大。当α较小时,系统频带利用率提高,噪声的影响减弱,但是时域波形衰减慢,系统的误码率增加。所以,从提高系统传输性能来讲,应将α的取值取大些;而从频带利用率来讲,应将α的值取小些。当α为0时,传输特性即为理想低通滤波,所需信道带宽最窄,这种信道当然是无法实现的。若α为1时,系统所占用频带最宽,是理想低通滤波器的2倍,其频带利用率为1。在卫星通信中,从带宽而言,希望取小一些。但α减小,眼图过零点波形过渡抖动加剧,会影响接收机定时最佳采样和整个系统的性能。。

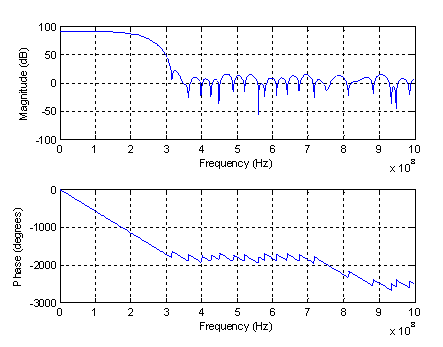

图1-4为用于基带成型的成型滤波器的幅频特性,采用平方根升余弦,滚降系数取α=0.35。对于成型因子为0.35的成型滤波器,其冲击响应持续时间一般为8个符号周期。因此在实际实现过程中,用8个符号数据与成型滤波器单位冲击响应进行卷积,由于系统采用了8倍符号采样,因此将成型滤波器的阶数设计为64阶。并通过MATLAB生成平方根升余弦滤波器系数。

图1-4 成型滤波器幅频特性

1.1.2.3内插成型多相滤波器

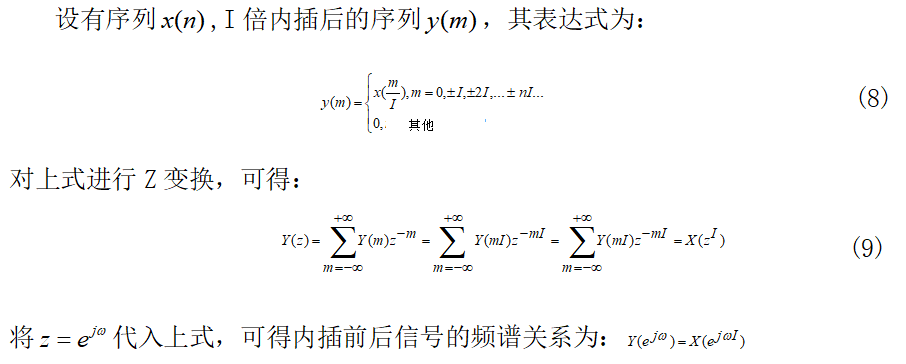

内插处理可在保持信号频谱不变的情况下提高采样率。数字内插最简单的方法就是在每个有效的输入采样点之间插入I-1(I是内插倍数)个零值,再通过低通滤波将零值采样点处的值转化为实际输入的近似值,从而使原信号采样率增加为原来的I倍。

从式中可以看出,内插后的信号频谱为原始序列频谱经I倍压缩后得到的谱。输出频谱中不仅含有原始的基带分量,而且还有频率大于的高频镜像分量。因此,需要对内插后的信号进行去镜像滤波即可恢复原始谱,去镜像滤波一般采用带宽为低通滤波器。可以看到,整数倍内插可以大大提高时域分辨率,进而提高信号的采样率。结合本方案的采样率设计要求,采用8倍符号内插处理。

传统的插值器是“先插值后滤波”,这使得后续的滤波器必须以更高的速率和数据吞吐率运行,给硬件设计带来了压力。同时,插值后相邻两个采样点之间引入L-1个零(插值因子为L),显然对这L-1个零的运算是没有必要的。因此,在本方案中,采用并行8路多相滤波器处理。8倍内插多相滤波器并行处理实现框图如图1-5所示。

图 1-5 8倍内插多相滤波器并行处理实现框图

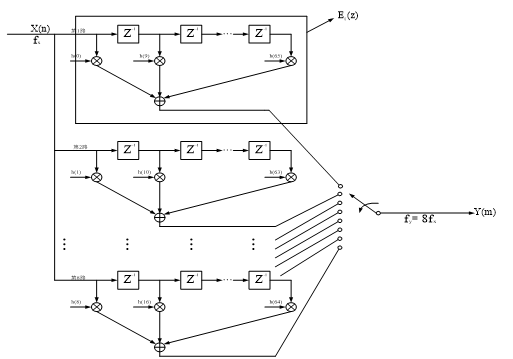

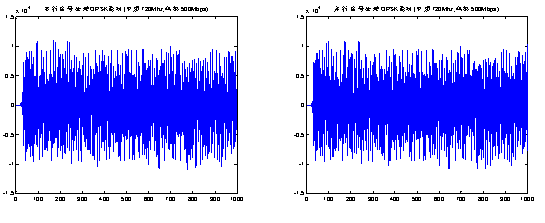

图1-6(a)、图1-6(b)分别为采用8倍内插多相滤波器8路并行处理MATLAB仿真I路、Q路成型滤波时域图。经与串行内插8倍仿真比较比对,结果相一致。

图1-6(a) I路8路并行内插多相成型滤波器

图1-6(b) Q路8路并行内插多相成型滤波器

1.1.2.4 数字正交中频调制

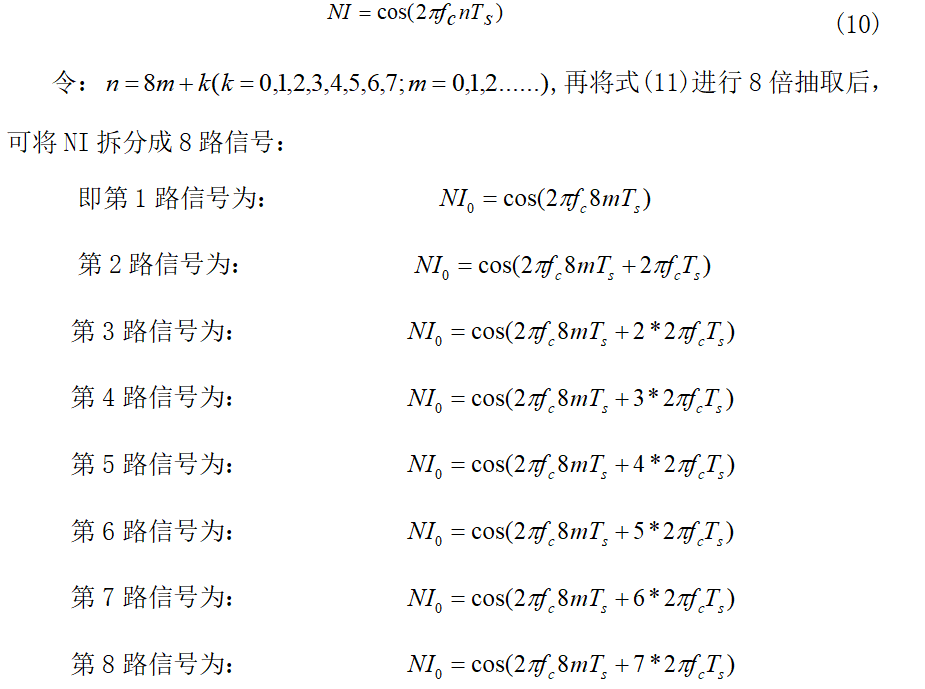

由于采用8路并行降速处理,需要对本振进行多相分解,分解的基本原理就是将高速率数据流拆分成8路并行的低采样速率数据流,若采样速率为,则每路信号的采样率为f s /8,假设正交端信号为:

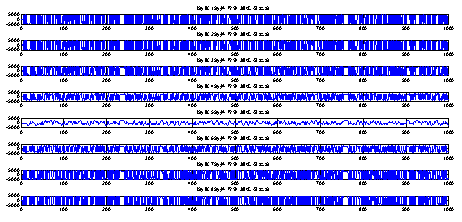

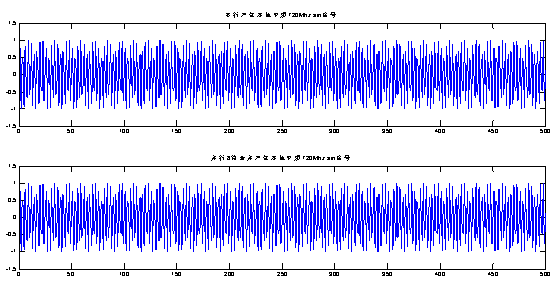

每一路通道的信号频率一致,区别只是在于初始相位值不同。正交端和同相端本振分别拆分成了8路,与之相乘的基带信号也必须拆分成8路才能相匹配。图1-7(a)、(b)分别为8路并行本地cos和sin Matlab仿真产生波形图。

图1-7(a)8路并行本地cos产生波形图(部分放大)

图1-7(a)8路并行本地sin产生波形图(部分放大)

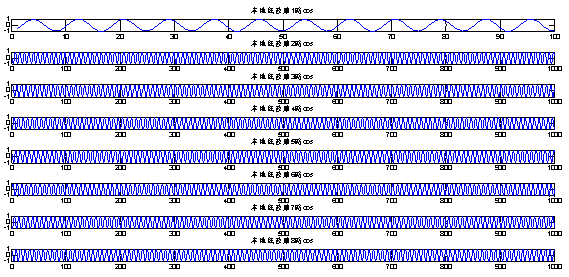

图1-8(a)、(b)分别为串行与8路并行产生本地cos和sin Matlab仿真产生波形图。经过比对,两者产生的波形是是一致的。

图1-8(a) 串行与并行8路产生本地cos信号波形(局部放大)

图1-8(b) 串行与并行8路产生本地sin信号波形(局部放大)

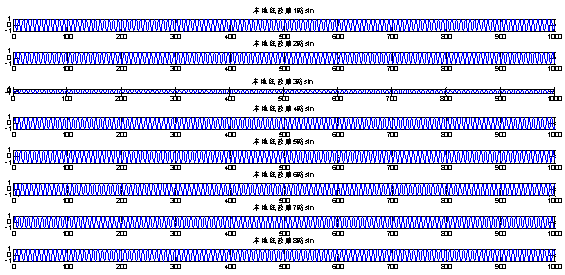

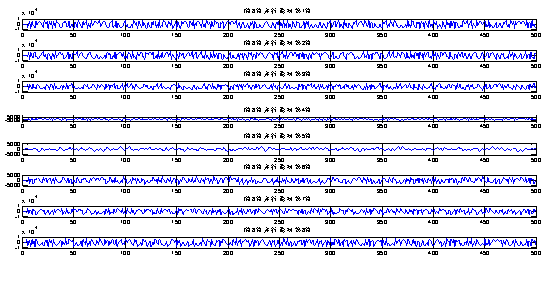

将本地产生的8路并行cos和sin信号分别与8路I、Q基带成型滤波后的输出数据作调制,实现QPSK调制。图1-9(a)、(b)分别为QPSK的并行8路I路调制和Q路调制。

图1-9(a) 并行8路I路调制波形(局部放大)

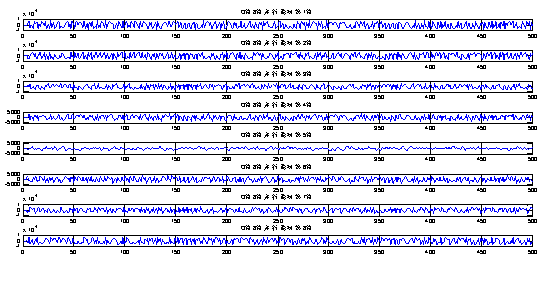

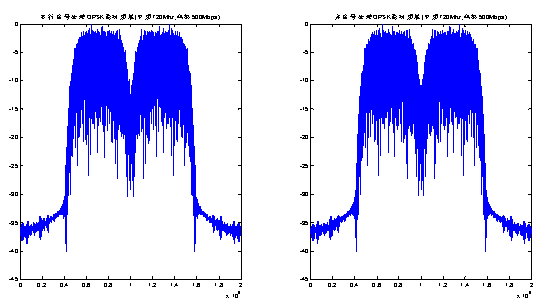

图1-10为QPSK采用串行调制和8路并行调制合并为一路的MATLAB仿真结果时域图,经比对,两者数据结果是一致的。图1-11为两者的频域仿真结果图。

图1-9(b) 并行8路Q路调制波形(局部放大)

图1-10 QPSK串行调制和8路并行调制合并时域图(局部放大)

图1-11 QPSK串行调制和8路并行调制合并频域图(局部放大)

1.1.2.5 OSERDES并串变换

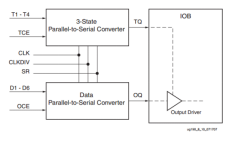

在完成8路并行QPSK调制后,需要采用FPGA的OSERDES模块进行并串变换,实现将8路250Mbps的数据,转换为2Gbps的串行数据给DA模块。

Xilinx Virtex系列FPGA具有OSERDES输出并串转换器逻辑资源,具有专门用来帮助实现源同步接口的待定时钟控制和逻辑资源。每个OSERDES模块包含一个用户数据和三态控制的专用串行器。数据和专用串行器都可以配置成SDR和DDR模式。

图1-12 OSERDES功能框图

在OSERDES并串转换过程中,并行数据串行化是从数据引入引脚的最低位到最高位的顺序进行的(即D1输入引脚上的数据传输到OQ引脚的首位)。OSERDES使用CLK和CLKDIV两个时钟进行数据速率转换。CLK是高速串行时钟。CLKDIV是分频并行时钟。

- 电子电路元器件套装与原理图解析:芯片分销商模式如何赋能电子设计2025-05-06

- 一种新型的基于仿真的MEMS结构进化方法2024-01-05

- 科研团队提出一种人工智能(AI)驱动的可穿戴面罩式自修复传感器阵列2024-01-05

- 如何解决冗长的if...else条件判断(上)2024-01-04

- 在单个器件上实现光电探测和神经形态视觉传感器两种角色的转换2024-01-04

- 如何解决冗长的if...else条件判断(下)2024-01-04